Flip-Flop Sequential Circuit

Last updated on May 14th, 2022 at 04:45 pm

This post covers Flip-Flop Sequential Circuit in detail with the help of a set of questions on the fundamentals of Flip-flop. Also, find answers to these. We hope, the Students who are interested to learn digital electronics and preparing for exams like GATE will find this post useful.

- Flip-Flop Sequential Circuit

- Calculate the frequency of a 4-bit ripple counter, if the period of waveform at the last flip-flop is 64 microseconds.

- What is the difference between edge-triggered and level-triggered flip-flop?

- Given the waveforms in Figure 1.a. for the D input and the clock, determine the Q output waveform if the flip-flop starts out RESET.

- What will be the output condition of a J-K flip-flop in toggle mode?

- Why are the D and J-K inputs called synchronous inputs of the flip-flops?

- Why are the preset (PRE) and clear (CLR) inputs called asynchronous inputs of a flip-flop?

- How does the flip-flop output get affected by its preset (PRE) and clear (CLR) inputs?

- Define edge-triggered flip-flop.

- Explain the difference between a flip-flop and a latch.

- What does it mean by the term SET and RESET in the context of flip-flop?

- Related posts (for further study) on Binary Counter

Flip-Flop Sequential Circuit

Here is a set of questions on flip-flop with answers.

Calculate the frequency of a 4-bit ripple counter, if the period of waveform at the last flip-flop is 64 microseconds.

In a 4-bit ripple counter, four flip-flops (FF0to FF3) are used. The input frequency of flip-flopFF0 is f and its output waveform frequency is f/2 which is applied as input of FF1.

Consequently, the output waveform frequency of FF1 is f/4 which is used as input of FF2. Then output waveform frequency of FF2 is f/8 which is used as input of FF3.

Therefore, the output waveform frequency of FF3 is f/16 and the time period is T=1/frequency=16/f.

Since the time period of the last flip-flop (FF3) is 64 microseconds,

T=16/f=64 x 10-6,

Then clock frequency of a 4-bit ripple counter is f=16/(64 x 10-6) Hz=250kHz.

What is the difference between edge-triggered and level-triggered flip-flop?

Edge-triggered flip-flops are edge sensitive, can store the input only when there is either a rising edge or falling edge of the clock signal. Level-triggered flip-flops are level sensitive and the output tracks the input when the enable input of flip-flop is high.

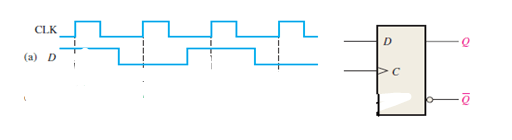

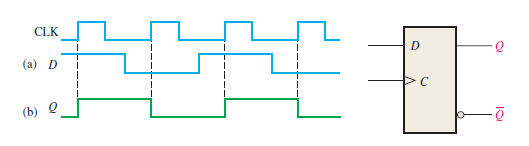

Given the waveforms in Figure 1.a. for the D input and the clock, determine the Q output waveform if the flip-flop starts out RESET.

Figure 1.a

Answer:

The Q output goes to the state of the D input at the time of the positive-going clock edge. The resulting output is shown in Figure1.b

What will be the output condition of a J-K flip-flop in toggle mode?

In the toggle mode, a J-K flip-flop changes the state on every clock pulse.

Why are the D and J-K inputs called synchronous inputs of the flip-flops?

For the flip-flops, the D and J-K inputs are called synchronous inputs because data on these inputs are transferred to the flip-flop’s output only on the triggering edge of the clock pulse; that is, the data are transferred synchronously with the clock.

Why are the preset (PRE) and clear (CLR) inputs called asynchronous inputs of a flip-flop?

Most integrated circuit flip-flops have two asynchronous inputs. They are normally labeled as Preset (PRE) and Clear (CLR), or direct set (SD) and direct reset (RD) by some manufacturers.

These are inputs that affect the state of the flip-flop independent of the clock, so they are called asynchronous inputs of a flip-flop. An active level on the preset input will set the flip-flop to the 1 state, and an active level on the clear input will reset the FF to the 0 state at any time, regardless of the conditions at the other inputs.

How does the flip-flop output get affected by its preset (PRE) and clear (CLR) inputs?

An active preset input (PRE) makes the Q output of flip-flop HIGH (SET) and an active clear input (CLR) makes the Q output of flip-flop LOW (RESET). These preset and clear inputs must both be inactive for synchronous operation. In normal operation, preset and clear would not be active at the same time.

Define edge-triggered flip-flop.

An edge-triggered flip-flop changes state either at the positive edge (rising edge) or at the negative edge (falling edge) of the clock pulse and is sensitive to its inputs only at this transition of the clock.

Two types of edge-triggered flip-flops are there. It can be either positive edge-triggered (no bubble at CLK input) or negative edge-triggered (bubble at C input). The key to identifying an edge-triggered flip-flop by its logic symbol is the small triangle inside the block at the clock (C) input. This triangle is called the dynamic input indicator.

Explain the difference between a flip-flop and a latch.

The main difference between latches and flip-flops is in the method used for changing their state. Flip-flops are edge-triggered or edge-sensitive whereas gated latches are level-sensitive.

The latch is a type of temporary storage device that has two stable states (bistable) and is normally placed in a category separate from that of flip-flops. Latches are similar to flip-flops because they are bistable devices that can reside in either of two states using a feedback arrangement, in which the outputs are connected back to the opposite inputs.

Flip-flops are synchronous bistable devices, also known as bistable multivibrators. In this case, the term synchronous means that the output changes state only at a specified point (leading or trailing edge) on the triggering input called the clock (CLK), which is designated as a control input, C; that is, changes in the output occur in synchronization with the clock.

What does it mean by the term SET and RESET in the context of flip-flop?

In the flip-flop, SET means that the Q output of the flip-flop is HIGH, and RESET means that the Q output of the flip-flop is LOW.

Related posts (for further study) on Binary Counter

Asynchronous Counter – study & revision notes

Synchronous Counter – Study & Revision Notes

How to design a Synchronous counter – step by step guide

2-bit Synchronous Binary Counter using J-K flip-flops

A 3-Bit Asynchronous Binary Counter – Up Counter

Asynchronous Up counter for Positive & Negative edge-triggered flip-flops

Binary Counter Sequential Circuit – FAQs

Frequently Asked Questions on Flip-Flops Sequential Circuit

Numerical problems on asynchronous counter & synchronous counter

J-K flip-flop – Frequently asked questions for semester & GATE exam

Modulus-M (MOD-M) asynchronous counter – Study and revision notes

Digital Electronics – Hub page

Author of this post

This post is co-authored by Professor Saraswati Saha, who is an assistant professor at RCCIIT, a renowned degree engineering college in India. Professor Saha teaches subjects related to digital electronics & microprocessors.