Synchronous Counter – Study & Revision Notes

In this post, we will study Synchronous Counter and its benefits over Asynchronous Counter. We will also study the differences between Synchronous Counter and Asynchronous Counter.

In binary Synchronous Counter, the flip/flops are clocked simultaneously. The output of all the flip-flops changes in synchronism with the clock input and hence, it is known as the synchronous counter.

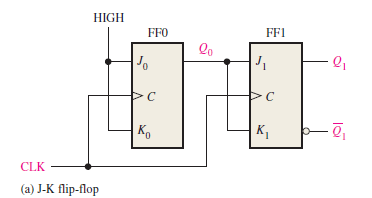

As shown in Figure 1 below, in a 2-bit synchronous counter the 2 flip/flops are clocked simultaneously, which means they are connected to the same clock input (CLK).

Figure 1: shows the clock connection in the synchronous counter.

What is a Synchronous Counter?

The term synchronous refers to events that have a fixed time relationship with each other.

A synchronous counter is one in which all the flip-flops in the counter are clocked at the same time by a common clock pulse. Synchronous counters are also known as parallel counters because all of the FFs are triggered simultaneously (in parallel) by the clock input pulses.

J-K flip-flops are used to illustrate most synchronous counters. D flip-flops can also be used but generally require more logic because they don’t have any direct toggle mode or no-change states.

What are the advantages of Synchronous Counter over Asynchronous Counter?

To find out the benefits and advantages of Synchronous Counter over Asynchronous Counter, we will first list down the problems found with asynchronous counters.

Problems found with asynchronous counter

- The problems encountered with asynchronous counters (or ripple counters) are caused by the accumulated F/F propagation delays. In other words, the FFs do not change states simultaneously in sync with the input pulses.

- Another problem encountered with the asynchronous counter is the glitches at the decoding gate outputs.

How does the Synchronous Counter solve the problems with the asynchronous counter?

The limitations of the asynchronous counter can be overcome with the use of synchronous or parallel counters in which all of the FFs are triggered simultaneously (in parallel) by the clock input pulses.

(Note: In asynchronous counter, the output of the previous flip-flop is the clock pulse input for the next flip-flop and hence, the delay is more and speed is less).

What are the notable differences between the circuit arrangements of synchronous counter with its asynchronous counterpart?

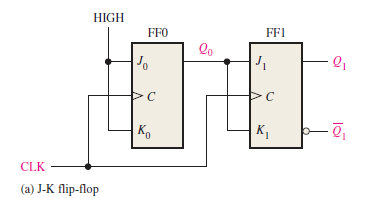

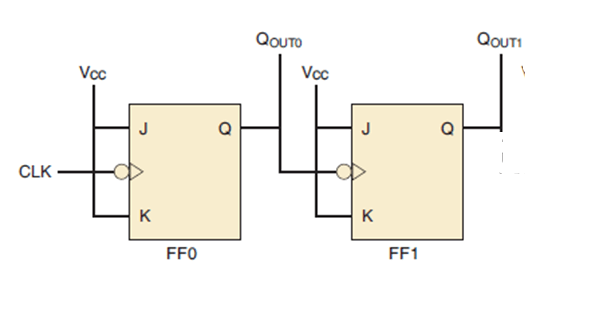

If we compare the circuit arrangement for synchronous counter (figure 2a) with its asynchronous counterpart (figure 2b) we can see the following notable differences:

- The CLK inputs of all of the FFs are connected together so that the input clock signal is applied to each FF simultaneously.

- Only FF0, the LSB, has its J and K inputs permanently at the HIGH (Vcc) level. The J, K inputs of the other FFs are driven by some combination of FF outputs.

- The synchronous counter requires more circuitry than does the asynchronous counter.

Figure 2a -Circuit arrangements of 2-bit synchronous counter

Figure 2b-Circuit arrangements of 2-bit asynchronous counter

Related Study:

How to Design a synchronous counter: a step-by-step guide

Author of this post

This post is co-authored by Professor S. Saha, who is an assistant professor in a renowned degree engineering college in India. Professor Saha teaches subjects related to digital electronics & microprocessors.