Direct Memory Access (DMA) in microprocessor

In this post, we will discuss the Direct Memory Access or DMA process, the role of HOLD and HLDA signal pins of microprocessors during DMA data transfer, the advantages of DMA operation, and different DMA data transfer modes.

Direct Memory Access | DMA

Direct Memory Access (DMA) is a special method of data transfer between input/output devices and memory bypassing the microprocessor. There are different data transfer methods available for data transfer between two processors or between a processor and an I/O device where the processor and system buses are involved. But in the DMA data transfer technique microprocessor allows the external device to transfer the data directly to/from memory without any interference of it.

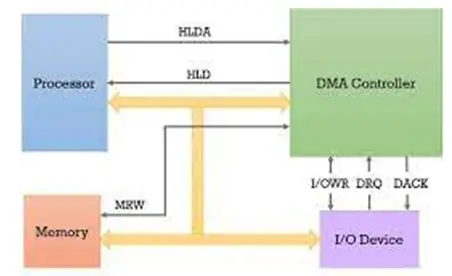

In the ‘Direct Memory Access’ or DMA data transfer mode the device requests the processor using a DMA controller to hold its data, address, and control bus. So the device is free to transfer data directly to/from the memory. The DMA data transfer is initiated only after receiving the acknowledgment signal from the microprocessor.

Sequence of Events in a DMA Process & Role of HOLD and HLDA signal

The sequence of events in a Direct Memory Access (DMA) process is as follows:

- When any external device wants to transfer data from the memory, the device has to send DMA request (DRQ) to the DMA controller.

- Then DMA controller asserts one of the request pins HOLD for holding the processor.

- Then the microprocessor completes its current instruction and enters into the hold state. In the hold state, the processor temporarily stops the execution of the instruction and releases the address and data buses by making them enter into a high-impedance state.

- The processor leaves control over the bus and acknowledges the HOLD request through the HLDA signal to indicate the release of bus control to the peripheral or the DMA controller.

- Finally, the DMA controller asserts both the MEMW’(memory write) and the IOR (I/O read) lines on the control bus.

- Direct memory access operation starts. The byte of data is then transferred directly from the I/O device to the memory location without passing through the processor or the DMA controller.

- Now the processor is in a HOLD state and the DMA controller has to manage the operations over buses between the CPU, memory, and I/O devices.

- Upon completion of the DMA operation, the DMA controller removes the HOLD signal applied to the processor and releases the bus control.

- The processor continues executing from where it left off in the program.

Figure 1: Schematics of the DMA process and the signal pins associated with the process.

Advantages of Direct Memory Access (DMA) operation

In normal programmed input/output data transfer techniques (for example in polled mode or in interrupt-driven data transfer mode) the processor becomes busy checking whether any input/output operation is completed or not for the next input/output operation. Therefore the processor is actively involved in the entire data transfer process. So, the data transfer rate is limited and the technique is slow.

This problem of slow data transfer between input-output devices and memory or between two memories is avoided by implementing Direct Memory Access (DMA) technique. This is faster as the processor is bypassed and the control of the address bus and data bus is given to the DMA controller.

Signals related to the DMA operation – Abbreviations and full forms

Abbreviations and full forms of signals related to the DMA operation are given below.

- HOLD – hold signal

- HLDA – hold acknowledgment

- DREQ – DMA request

- DACK – DMA acknowledgment

DMA Data Transfer Modes | Data transfer modes of DMA

DMA data transfer can be divided into two modes:

- Burst Mode or block transfer mode

- Cycle Stealing Mode or interleaved mode

During the DMA data transfer, the processor can perform only those operations in which it doesn’t require the access of the System Bus which means mostly the processor will be in the blocked state.

Burst Mode

In the burst mode of DMA data transfer, a complete block of data is transferred in a single DMA cycle. The system bus is released by the peripheral or DMA controller only after the required bytes of data are transferred.

Cycle Stealing Mode

In the cycle-stealing mode of DMA data transfer, a complete block of data is transferred over many DMA cycles. The system bus is released to the processor after a byte or a set of bytes is transferred in one DMA cycle. Thus, the processor is not suspended from its activities for a long time. It takes several DMA cycles to complete the transfer of one block of data.

DMA – FAQ

Direct Memory Access (DMA) is a special method of data transfer between input/output devices and memory bypassing the microprocessor.

Direct Memory Access

Direct Memory Access

DMA data transfer can be divided into two modes: Burst Mode or block transfer mode and Cycle Stealing Mode or interleaved mode.

Author of this post

This post is co-authored by Professor Saraswati Saha, who is an assistant professor at RCCIIT, a renowned degree engineering college in India. Professor Saha teaches subjects related to digital electronics & microprocessors.