Irregular Sequence Counter

Last updated on July 21st, 2023 at 09:58 am

In this post on Irregular Sequence Counter, we will design a counter for an irregular sequence using J-K flip-flops with step-by-step analysis.

Irregular Sequence Counter design

Problem statement: Design a counter to generate the following irregular sequence 0->2->5->4->7->0 using J-K flip-flops.

Design Solution: Let’s design the counter using J-K flip-flops.

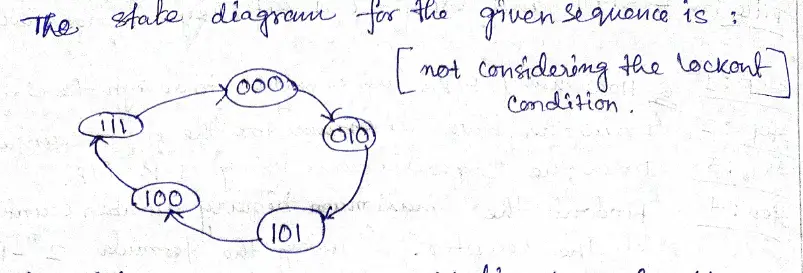

Step1: State diagram for the given sequence 0->2->5->4->7->0 is

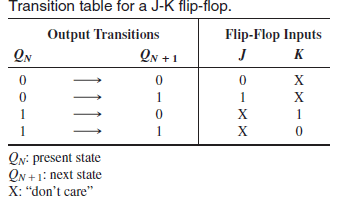

Step2: Choose the flip-flop and write the transition table for the same flip-flop

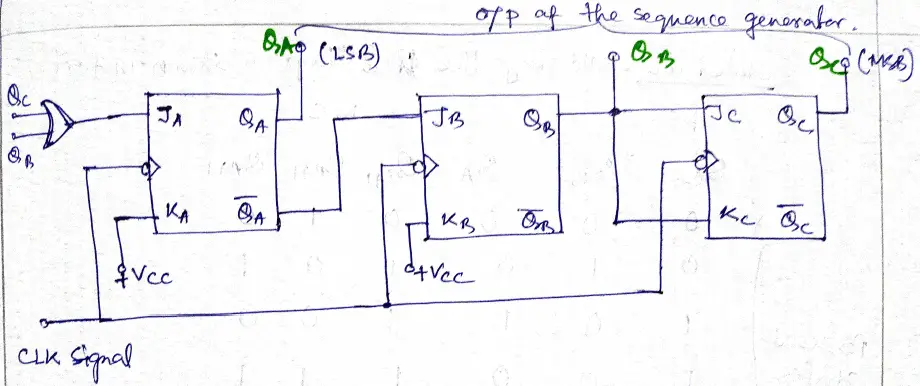

Three J-K flip-flops are required because it is a 3-bit counter (output QCQBQA).

J-K Transition Table is given below:

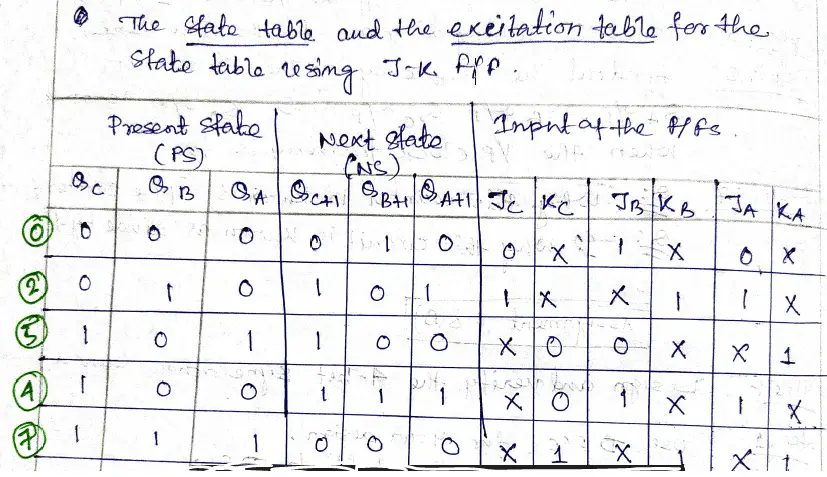

Step 3: Draw the state table and the excitation table for the state diagram using J-K flip-flops.

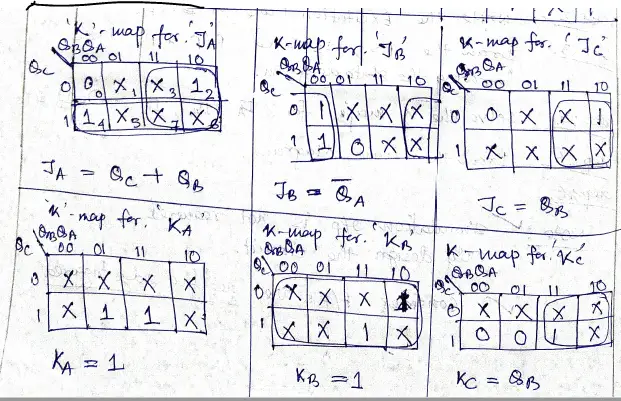

Step 4: Solve the K- map to get the reduced expression for each flip flop input. For the min-terms 0, 2, 5, 4, and 7 get the output from the above table but for the unused state ( 1,3,6)consider the output as don’t care(X).

Step 5: Implement the logic circuit with J-K flip-flop and logic gates.

You can also refer to the following related posts for further study:

Author of this post

This post is co-authored by Professor Saraswati Saha, who is an assistant professor at RCCIIT, a renowned degree engineering college in India. Professor Saha teaches subjects related to digital electronics & microprocessors.