Opcode fetch machine cycle in 8085

The Opcode fetch machine cycle is the first step in the execution of any instruction. In this cycle, the microprocessor reads the opcode of an instruction from the memory. The control and status signals for this machine cycle are IO/M’ = 0, S0 =1, and S1 = 1. This differentiates it from the memory read machine cycle. Every instruction has a one-byte opcode which is stored in the memory. Hence, every instruction execution starts with the opcode fetch machine cycle.

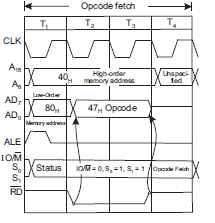

Opcode fetch machine cycle in 8085: step-by-step execution of an instruction with timing diagram.

Problem statement: Say, at the program memory location 4080, the instruction MOV B, A (opcode 47H) is stored while the accumulator content is FFH. Illustrate the execution of this instruction by timing diagram.

Solution:

Since the program counter sequences the execution of instructions, it is assumed that the PC holds the address 4080H.

While the system executes the instruction, the following process takes place one after another.

Figure 1 shows the execution of the above. It consists of 4T states.

Step1

The CPU places the address 4080H (residing in PC) on the address bus—40H on the high order bus A15 – A8 and 80H on the low order bus AD7 – AD0.

Step2

The CPU raises the ALE signal to go high. The H to L transition of ALE at the end of the first T state (T1) de-multiplexes the low order bus.

Step3

The CPU identifies the nature of the machine cycle by means of the three status

signals IO/M’, S0, and S1 (IO/M’ = 0, S1 = 1, S0 = 1).

Step4

In the second T- state (T2), memory is enabled by the signal.

The content of the 4080H memory location i.e., 47H is placed on the data bus. PC is incremented to 4081H automatically.

Step5

In the third T- state (T3), the CPU reads 47H and places it in the instruction register.

Step6.

In the fourth T- state(T4), the CPU decodes the instruction, places FFH (accumulator content) in the temporary register, and then transfers it to register B.

Author of this post

This post is co-authored by Professor Saraswati Saha, who is an assistant professor at RCCIIT, a renowned degree engineering college in India. Professor Saha teaches subjects related to digital electronics & microprocessors.