## Peripheral Interface IC 8255

## Microprocessor and Micro-Controller

Course Material - EC 403

- Functional description of Pins

- Programming the PPI

- Modes of Operation

- Interfacing with 8085

By

Er. Mrs. Saraswati Saha, Assistant Professor, ECE Department,

**RCCIIT**, Kolkata

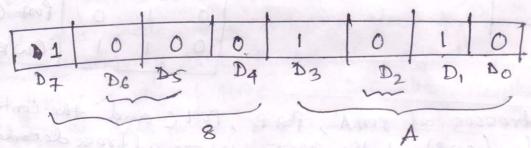

has been 'interfaced' to three I/O devices using the 8255 as a temporary storage space Thus, the 8255 has three sets of '8-bit parallel ports', which act as intermediary between a processor and a number of I/O devices. Note that in all cases the I/O devices used only 8-bit data capability - so, only the lower data lines D0-D7 are connected to the

However, it is a 'programmable chip' as are all the chips we will learn in the next chapters as well. Keep in mind that these 'interfacing chips' do not have any 'processing ing' capability. They can only be made to act in the way we want to by 'programman it using the instructions of 8086 (i.e., the processor to which it is connected). However they have the hardware to do the special functions that are needed for each specific pure pose. Programming interfacing chips entails writing of 'control words' in their comme command registers. We will learn this idea, starting with the 8255.

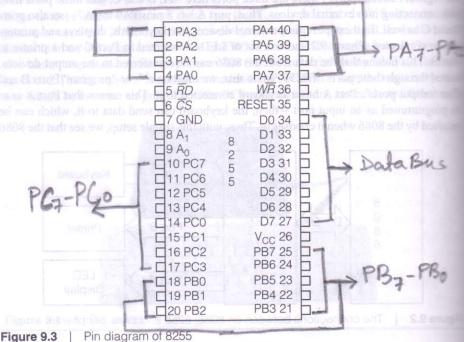

## 9.2.1 | Pin Configuration and Internal Block Diagram

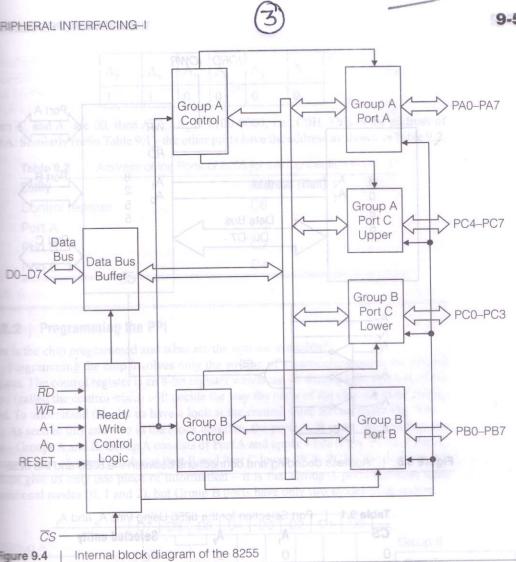

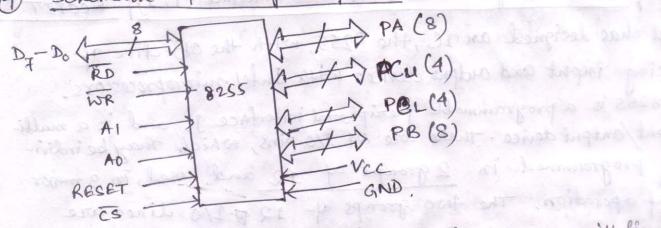

Figure 9.3 shows the pin configuration of the DIP (dual-in-line) version of the chip. see that it has 40 pins, which consist of three 8-bit ports named Port A (PA), Port B and Port C (PC), each of which can be programmed as input or output ports. Figure shows the internal block diagram of the chip. It is seen to consist of various functional blocks, and let us take a quick look at each of the blocks.

Data Bus Buffer There is a three state bi-directional 8-bit buffer which is used to interface the chip to the data bus of the system. Upon execution of the processor's input or our instructions, data and control/status words are received or transmitted by the buffer.

Read/Write Control Logic It manages all data transfer between the chip and processor on accepting control signals from the control and address buses of the system

Bus Data Bus Buffer Read/ Write An Control Logic RESET Internal block d Figure 9.4

Boup A and B Controls Funct have their corresponding c The way the chip is to act i sich can be written to and rea and an 8255 in Fig. 9.5. The low bus of the 8086. The RD a the 8086. If this chip (whi an eight-bit address, only the be involved in the address de Merwise, 16 address lines may greater than 16 bits.) Any t pins A, and A, of the 8255.7 this chip, and each one nee binations of these two lines

Scan

as a temporary storage space ch act as intermediary between cases the I/O devices used have D7 are connected to the 8255 ps we will learn in the next two ips' do not have any 'processwe want to by 'programming nich it is connected). However e needed for each specific purcontrol words' in their control the 8255.

## ram

n-line) version of the chip. amed Port A (PA), Port B (FE put or output ports. Figure 9o consist of various functional

buffer which is used to interface the processor's input or out transmitted by the buffer.

fer between the chip and nd address buses of the system

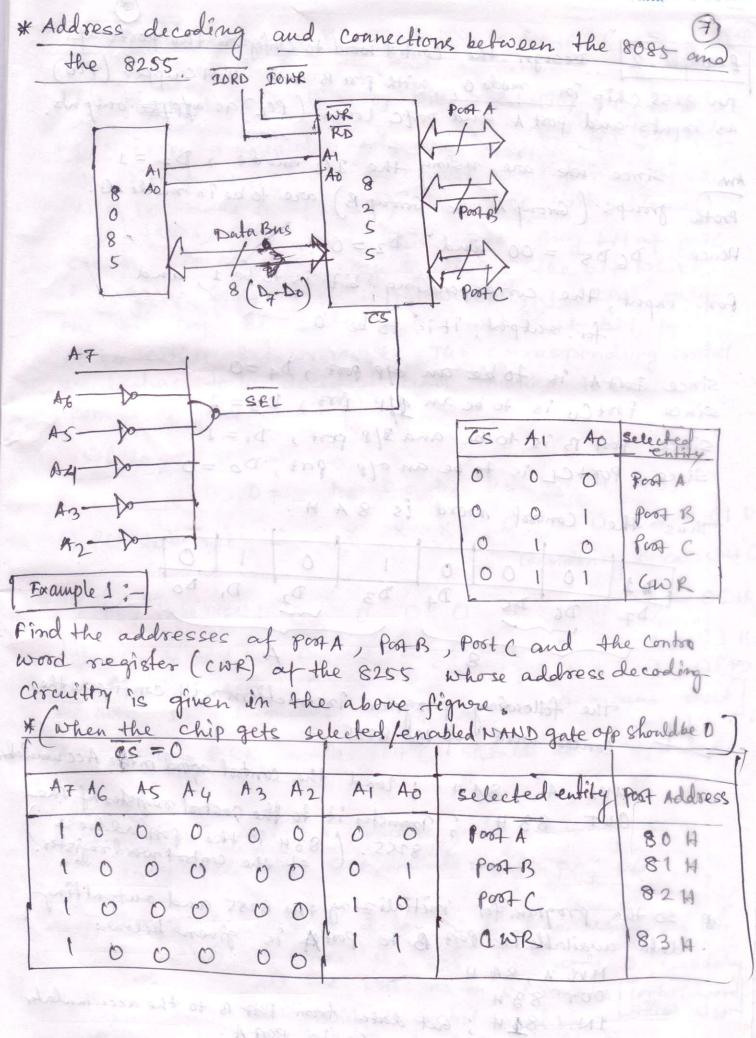

Functionally, this chip has been divided as Group A and B and have their corresponding controls. We will soon see what this grouping is intended The way the chip is to act is decided by a register called the control/status register, which can be written to and read from. Now see a typical connection between the 8086 an 8255 in Fig. 9.5. The lower data lines of the chip can be connected to 8 bits of the bus of the 8086. The  $\overline{RD}$  and  $\overline{WR}$  are connected to the  $\overline{IORD}$  and  $\overline{IOWR}$  generated the 8086. If this chip (which is viewed as an I/O port by the processor) is to have an eight-bit address, only the lower 8 lines of the address lines of the processor need  $\overline{CS}$  line to be activated. Merwise, 16 address lines may be used. (Recollect that no I/O port can have an address greater than 16 bits.) Any two address pins of the processor are to be connected to pins A<sub>0</sub> and A<sub>1</sub> of the 8255. This is because there are four separate entities associated this chip, and each one needs a unique address. This is achieved by the four possible binations of these two lines, as shown in Table 9.1.

If we see the internal structure of the IC, we will find that, in addition with the three 8-bit 40 posts, that, in addition with the three 8-bit 40 posts, there is another register called control register or control word register (CWR).

To identify the 3 perts and control register, the 8255 uses two address lines - to and A1, these lines gets their signals from the 8085 processor address bus. The identification of the ports and negister are based on the Ao and A1, is given in Table!

| AI | Ao ,       | selected.     |

|----|------------|---------------|

| 0  | 0          | Post A        |

| 0  | (See 6 21) | POTT 15       |

| 1  | 0          | POST C        |

| 1  | 1          | control regis |

Programming the PPI programming the chip involves only the writing of a particular word to the control register.

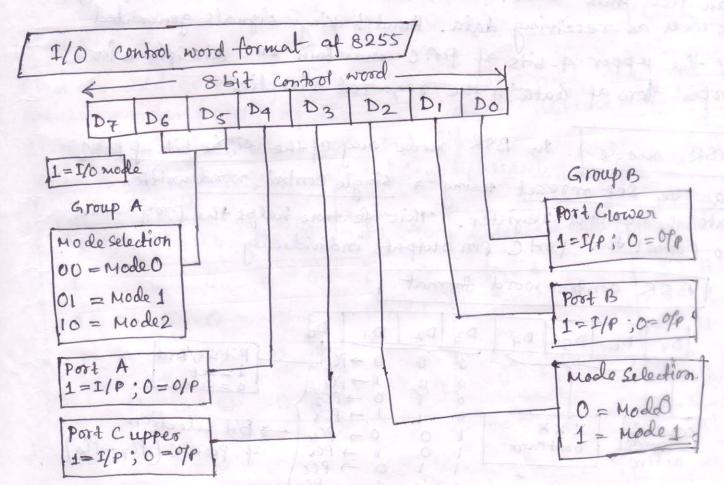

The control register is an 8-bit register which can be written into. The bits of this word (called the control written into. The bits of this word (called the Chip one word) will decide the way the posts of the Chip one word) will decide the way the posts of the Chip one word will decide the way the posts of the chip one word this, Let us have to be configured. To understand this, Let us have a look at the control word format.

Bit Assignment of the control word. (5)

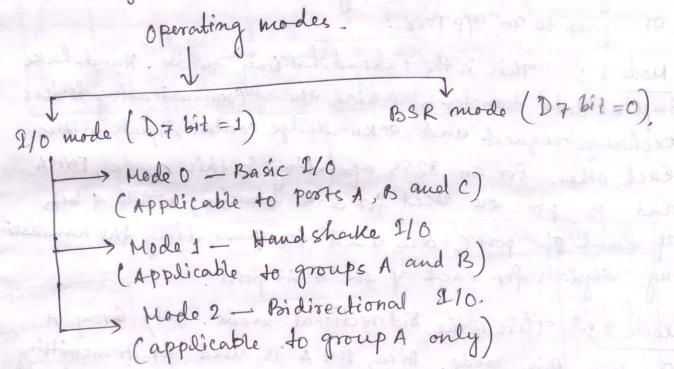

first, look at D7bib) it suggests the options of No mode or BSR (bit set reset) mode. I/O mode is the normal mode of operation and BSR is a special mode catering to post c alone

Mode 0: This is the simplest and most widely used mode. In this mode, the two 8-bit posts A and B and the 4-bit posts post Crepper and Post Crower may be used independ posts post Grepper and Post Crower may be used independ ently. Here, data is simply taken in John an I/P Post or given to an ofp post.

Mode 1: This is the e chandshaking's mode. Handshake simplies data transfer in which the Communicating devices exchange request and acknowledge control signals with each other. For an 8255 aperating in this mode, ports A and B pins are used for data transfer, while 4 bits af each of post C are used for generating the handslatter ug signals for each of the 8-bit posts.

Mode 2 r This is the bidirectional mode. Only Group A Can use this mode. Here, Post A is rised for Fransmitting as well as receiving data. Handshaking signals generated by the upper 4-bits of Post C. maintain bis discipline for proper flow of data in the required direction.

BSR mode In BSR mode, any of the eight bits of Port C can be Set or reset resing a single control word written into the control register. This feature helps the programmer, to control the port C. pin outputs individually.

BSR control word format

| INT DG          | D5 D4               | D3 D2 | Di Da                                                          | Bit Set/Resel                      |

|-----------------|---------------------|-------|----------------------------------------------------------------|------------------------------------|

| TO TO           |                     | 0 0   | $0 \rightarrow PC_0$ $1 \rightarrow PC_1$ $0 \rightarrow PC_2$ | 1 = set<br>0 = Reset               |

| 0 = BSR<br>mode | X X X<br>Don't care | 100   | 0 -> PC4 -                                                     | -> Bit Selection of Post-C(Plz-Ple |

| active 1        | DOS MELTINA A       | 1 1   | 0 -> PC4                                                       |                                    |

Example 12 Design the control word to configure the poots of an 8255 chip in mode 0, with post B and Post Cupper (Plu) as inputs and post A and post Coas (PCL) as affects outputs.

Ams. Since we are using the 210 mode, D7 =1 Broth groups (Group A & Group B) are to be in made O. Hence, D6 D5 = 00 and D2 = 0.

for input, the corresponding bit is to be 1, and for output, it is to be 0.

Since PortA is to be an off post, DA =0 since Post Cu is to be an #p Post, D3 = 1 Since post B is to be and IfP post, Di=1 Since PortCL is to be an ofp port, Do =0.

Thus the control word is 8 A H.

the following program instructions will configure the control wood of the 8255.

MVI A, 8AH; load the control word in the Accumulator. OUT 83 H; Fransfer it to the control negister of the 8255. (83 H is the past address ) at the control wood register.

\* so the program for initializing the 8255 and outpatting data available in Post B to post a is given below:

MV2 4, 8A H

OUT 83 H

Get data form Post B to the accumulater More it to part. OUT 80 H

(1) PCo to be set (ii) PC7 to be reset (iii) PC1 to be set Ans This is a special mode and is applicable only for the kits at Post C. In the control word format, if the mode takes effect. In this mode, any bit of Post C can be set or reset by specifying the bit which has to be set or reset. However, at a time, only one bit can be addressed - and that bit is to be either Set or reset. The corresponding control word has to be decided and moved to the. control register (CWR).

Solution: D3 D2 D1 Do. D6 D5 D4 0 0 6 1 = 01 # XXX Considering X' cares as O. i) PCo to be set: 0

11) PC7 to be reset: 0 0 0 0 1 1 1 0 = OEH (ii) PC1 to be set: 0 0 0 0 0 0 1 1 = 03 H. (v) PCF to be set 10 000 0 1 11 1 = OFF)

\* Here Do = 1 means Set; & Do = 0 means reset]

\* In the BSR made PORC Should be in Ofpmade.

Jup 9:- Generate a square pulse having 50% dutycycle in BER mode using PC7 Pin.

1) write a delay subrouline using keg Pair.

2) Configure the 8255 in mode 0, considering all the posts as in ofp mode [control word]

3) Then Abrite the control word to Set PC7 Pin 2 to reset PC7 Pin.

toad control word into accumulator to configure 8255 in mode 0. and are parts are in off mode. MVI A, 80 H. OUT CWR roop! MVI A, OFH; control word to set the OUT CWR CALL DELAY MVI A, OE; control word to neget the ; [CWR POST Add 1) OUT CWR CALL DELAY

JMP 200p

Subsontène prog:

0 = 1 0 0 0

Delay prog. using Reg. Pair.

Remarks: you will get a segnare pulse at point PCz.

opt time af the pulse will be of equal width.