# 8085 Interrupts

# Microprocessor and Micro-Controller

Course Material – EC 403

By

Er. Mrs. Saraswati Saha, Assistant Professor, ECE Department,

**RCCIIT**, Kolkata

010101 <u> 1010</u> Saraswati Saha Asst. Prof. ECE/RCCIIT EC-403 Topic: 8085 Interrupts Interrupt is a mechanism by which the processor (CPU) -101C is made to transfer control fromits current program -101C execution to another program af more importancepr higher priority. 01010 In general, interrupts are generated by a variety of sources, either internal or external, to the CPU. 1/p and ofp devices obtain the service of the CPU by using the interrupt Process. <del>0</del>101C ISR ( Interrupt service routine); The program or the routine that is executed upon interrupt is called intermet 0101C service vontine (ISR). After execution of the ISR, the processor must return to the interrupted program. -101C IVA ( The address of the memory where the ISR is located 1010 for a particular interrupt signal, is called interrupt vector JIDIC address (IVA) 010101 Types at Interrupts Interrupts are classified based on their maskability [] [][ interrupt vector address, and Source. -101C Classification based on Maskable Interrupts (RST 7.5) RST 6.5 RST 5.5 01C 0 010 Maskability: DIDIC > Non-maskable interrupts. (TRAP) 01010 The 8085 up includes four maskable interrupts and one wormaskable inferrupt. The microprocessor can [] [][ U ignore or delay a maskable interrupt request if it is 4010 performing some critical task. However it has to <del>0</del>101 respond to a non-maskable interrupt request immediately. saher 01010 Date : 17/3/2020 Signature : ... 01010

Sonaswat ASST. Prof. ELE/RCCIIT/ Classification vectoried interrupte (TRAP, RST 7.5, RST 6.5, RSTS.5) 010 Based on interrupt vector address Non - vectored Interrupte -101C ( INTR Vectored interrupts chave fixed interrupt vector address for ISRs where as for non-vectoried interrupts require external H/W to supply a call location to restart the execution Interrupt Vectoraddress Maskable or non-Interrupt--101C - maskable Non-maskable TRAP 0024 H 003C Maskable RSTFS 0034 RST6.5 Maskable 14 Maskable 002C H RST 5.5 Decided by external Maskable INTR · 🖻 🛛 🕻 HAN \* five interrupts only RST 7.5 interrupt-Among these Level-triggered, [ is four are edge-triggere and other Software interrupts Classification Based (RSTO -> RST7) their source Hardware mterrupts (TRAP, RSTZ.S, RSTG.S, RSTS.S, INTR, 1015 software interrupts are special instructions, which after execution transfer the control to a predefined ISR These instructions are included in the program by the Ex: For. RST1, CALL Locationis 00084 programmer. Ho interrupts are signals given to the processor, for recognition as an interrupter and execution of the corresponding ISR. There are five signal pins in 8085 up 2 s. saha [] Date : . 19/03/2020 Signature : ..... 01010

Questions \* 7 w.a.p. to enable all the interroupts in 8085 after rece \* 6> Explain the function of instructions (a) EI (b) DI (c) SIM (d) RIM. 010 1) Q. Explain the interrupt process in 8085 up. Ans. (R. Gaonkar Pg. 377) 2) Q. Define the following terms. (a) ISR (b) IVA 11 010 (C) H/W interrupt (d) s/w interrupt (e) vectored interrupt (f) Non-vectored interrupt 1010 Maskable interrupt (h) Non-maskable mterrupt. Ans. (Note) 1010 3) a, what is meant by priority of interrupt ? Interrupt priority decides which interrupt I 010 must be serviced when more than one interrupt is 1:010 sensed by the processor 11 010 priority. Interrapt and garretai relation (Highest priority) TRAP RSTTS 2. RST 6.5 3. 1010 RST S.S INTR (Lowest priority) 5. 1010 what is the location of ISR for RST S.S interrupt. 1 010  $(5.5 \times 8) = 44_{10}$   $(44)_{10} \rightarrow (20)_{H}$ 1010 " CALL location ~) 002CH ( 010 s) The concept of priority does not apply to s/winterrupts. 1010 Why ? As they are inserted into the program as instructions. nn Am. by the programmer and executed by the processor when the respective program lines are read. UI 1010

180 Microprocessors and Microcontrollers

# ★ 5.11 MASKING OF INTERRUPTS

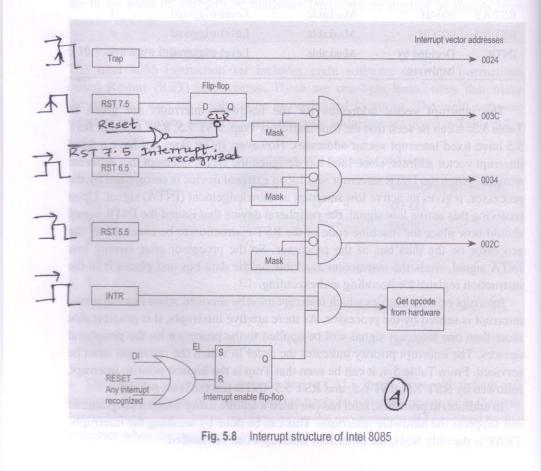

Masking can be done for the four hardware interrupts RST 7.5, RST 6.5, RST 5.5, and INTR. The masking of 8085 interrupts is done at different levels. Figure 5.8 shows the organization of hardware interrupts in the 8085. The figure clearly shows that TRAP is an NMI. RST 7.5 interrupt alone has a flip-flop to recognize its edge transition. The masking of interrupts can be done using SIM instruction. In addition, a separate interrupt enable flip-flop is available to mask or allow the interrupts. Figure 5.8 is explained in detail by the following five points.

- (i) The maskable interrupts are, by default, masked by the Reset signal. So no interrupt is recognized by the hardware reset.

- (ii) The interrupts can be enabled by the execution of the EI instruction. So to enable the interrupts after resetting the processor, the EI instruction must be used.

- (iii) The three RST interrupts can be selectively masked by loading the appropriate word in the accumulator and executing the SIM instruction. This is called *software masking*.

- (iv) All the maskable interrupts are disabled whenever an interrupt is recognized. So, it is necessary to execute the EI instruction every time the interrupts are recognized and serviced by the processor.

All the n This ins the inter be execu

stt.1 SIM Ins

The SIM inst memory. The end according menuted after if the contro memory is a second memory of the second memory is a second memory of the second memory of

Bit positio

The least three RST in the interrupts provided in t three bits mo

Ignored by th As alread flip-flop is u RST 7.5 inte In additio

can send seri in the MSB of D6 bit 1.

5.11.2 RIM In The RIM inst of the intern data stored i Table 5.7. The lease instruction in

of the bit 1 i

All the maskable interrupts can be disabled by executing the DI instruction. This instruction resets an interrupt enable flip-flop in the processor and the interrupts are disabled. To enable interrupts, EI instruction has to be executed.

#### 11.1 SIM Instruction

The SIM instruction is used to mask or unmask the restart (RST) hardware merupts. The SIM instruction when executed reads the contents of the accumulator and accordingly masks or unmasks the interrupts. So the SIM instruction must be executed after storing the appropriate control word in the accumulator. The format of the control word to be stored in the accumulator before executing the SIM instruction is shown in Table 5.6.

| Table 5.0 Accumulator bit pattern for Silvi instruction |               |                                                   |      |                  |                     |              |              |              |

|---------------------------------------------------------|---------------|---------------------------------------------------|------|------------------|---------------------|--------------|--------------|--------------|

| Bit position                                            | D7            | D6                                                | D5   | D4               | D3                  | D2           | D1           | DO           |

| Name                                                    | SOD           | SDE                                               | X    | R7.5             | MSE                 | M7.5         | M6.5         | M5.5         |

| Explanation                                             | data<br>to be | Serial data<br>enable—<br>set to 1 for<br>sending | used | RST<br>7.5 flip- | enable—<br>Set to 1 | 1 to<br>mask | 1 to<br>mask | 1 to<br>mask |

Table 5.6 Accumulator bit pattern for SIM instruction

The least significant three bits D2–D0 are used to individually mask the bree RST interrupts, as shown in Table 5.6. These bits are made 0 to unmask the interrupts and 1 to mask the interrupts. In addition, a master control is also provided in the D3 bit. This bit must also be set to 1 to make the least significant three bits meaningful. Otherwise, the data in the least significant three bits are grored by the processor.

As already discussed, the <u>RST 7.5 is an edge-triggered interrupt and a separate</u> flip-flop is used to recognize it. This flip-flop can be reset, thereby ignoring the <u>RST 7.5 interrupt</u>. This is done by making the D4 bit 1.

In addition to masking interrupts, the SIM instruction has another function. It can send serial data on the SOD line of the processor. The data to be sent is placed in the MSB of the accumulator and the serial data output is enabled by making the D6 bit 1.

#### 5.11.2 RIM Instruction

The RIM instruction is used to read the status of the interrupt mask bits. When the RIM instruction is executed, the accumulator is loaded with the current status of the interrupt masks and the pending interrupts. The format and meaning of the data stored in the accumulator after execution of the RIM instruction is shown in Table 5.7.

The least significant three bits of the accumulator after executing RIM instruction indicate whether the RST hardware interrupts are masked. The presence of the bit 1 indicates that the corresponding interrupt is masked.

5

6.5

interrupts 7.5

5.5

182 Microprocessors and Microcontrollers

| Bit position | D7                             | D6                          | D5                          | D4                          | D3                                          | D2                         | D1                         | DO                         |

|--------------|--------------------------------|-----------------------------|-----------------------------|-----------------------------|---------------------------------------------|----------------------------|----------------------------|----------------------------|

| Name         | SID                            | 17.5                        | 16.5                        | 15.5                        | IE                                          | M7.5                       | M6.5                       | M5.5                       |

| Explanation  | input<br>data<br>in the<br>SID | if RST<br>7.5 is<br>pending | if RST<br>6.5 is<br>pending | if RST<br>5.5 is<br>pending | Set to 1 if<br>interrupts<br>are<br>enabled | if RST<br>7.5 is<br>masked | if RST<br>6.5 is<br>masked | if RST<br>5.5 is<br>masked |

Table 5.7 Accumulator bit pattern after execution of RIM instruction

All the hardware interrupts can be masked by executing the DI instruction. To check whether the interrupts are enabled or disabled, the programmer can check the D3 bit of the accumulator after executing the RIM instruction. If the D3 bit is set to 1, it means that the interrupts are enabled. The bits D4–D6 indicate whether there are any RST interrupts pending. Logic 1 on these bits indicates that the corresponding interrupts are pending.

In addition to reading the interrupt mask, the RIM instruction is also used to read the serial data on the SID pin of the processor. The data on the SID pin is stored in the MSB of the accumulator after execution of the RIM instruction.

#### Example:

Write the assembly language program lines to enable all the interrupts in the 8085 after reset.

After reset, all the interrupts are disabled as shown in Fig. 5.8. So, the EI instruction must be executed. To enable all RST interrupts, the corresponding bits in the accumulator pattern must be 0 and the Mask Set Enable bit must be 1 before executing the SIM instruction.

| EI               | ; | Enable interrupts.                             |

|------------------|---|------------------------------------------------|

| MVI A, 00001000B | ; | Unmask the interrupts.                         |

| SIM              | ; | Set the mask and unmask using SIM instruction. |

## 5.12 TIMING OF INTERRUPTS

The interrupts are sensed by the processor one cycle before the end of execution of each instruction. An interrupt signal must be applied long enough for it to be recognized. The longest instruction of the 8085 takes 18 clock periods. So, the interrupt signal must be applied for at least 17.5 clock periods. This decides the minimum pulse width for the interrupt signals.

6

The maximum pulse width for the interrupt signals is decided by the condition that the interrupt signal must not be recognized once again. This is under the control of the programmer. Once an interrupt is recognized, all interrupts are disabled. The re-enabling of interrupts is done by executing the instruction EL So, the maximum duration for the interrupts is decided by the execution of the EI instruction. The interrupt signal must be removed before the EI instruction is executed so that it will not be recognized once again.

## Any EI instru the start complet

# 5.13 IN

INTR int address. 1 how the in interfacin, INTR requ active low places it in Fig. 5.9 sh fata bus w the opcode

States of the st

timing of

Fig. 5.10. The

nucles. The fit